## INTEGRATED CIRCUITS

Product data Supersedes data of 1994 Dec 15

2002 Dec 17

### 74ABT5074

#### **FEATURES**

- Metastable immune characteristics

- Pin compatible with 74F74 and 74F5074

- Typical f<sub>MAX</sub> = 200 MHz

- Output skew guaranteed less than 2.0 ns

- High source current (I<sub>OH</sub> = 15 mA) ideal for clock driver applications

- Output capability: +20 mA / -15 mA

- Latch-up protection exceeds 50 0mA per Jedec Std 17

- ESD protection exceeds 2000 V per MIL STD 883 Method 3015 and 200 V per Machine Model

#### DESCRIPTION

The 74ABT5074 is a dual positive edge-triggered D-type flip-flop featuring individual data, clock, set and reset inputs; also true and complementary outputs.

#### QUICK REFERENCE DATA

Set (SDn) and reset (RDn) are asynchronous active-LOW inputs and operate independently of the clock (CPn) input. Data must be stable just one set-up time prior to the LOW-to-HIGH transition of the clock for guaranteed propagation delays.

Clock triggering occurs at a voltage level and is not directly related to the transition time of the positive-going pulse. Following the hold time interval, data at the Dn input may be changed without affecting the levels of the output.

The 74ABT5074 is designed so that the outputs can never display a metastable state due to set-up and hold time violations. If set-up time and hold time are violated the propagation delays may be extended beyond the specifications, but the outputs will not glitch or display a metastable state. Typical metastability parameters for the 74ABT5074 are:

$$\tau \cong 94 \ ps$$

and  $T_o \cong 1.3 \times 10^7 \ sec$

where  $\tau$  represents a function of the rate at which a latch in a metastable state resolves that condition and  $T_0$  represents a function of the measurement of the propensity of a latch to enter a metastable state.

| SYMBOL                               | PARAMETER                            | PARAMETER CONDITIONS<br>T <sub>amb</sub> = 25 °C; GND = 0 V |            |    |  |

|--------------------------------------|--------------------------------------|-------------------------------------------------------------|------------|----|--|

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>CPn to Qn or Qn | C <sub>L</sub> = 50 pF; V <sub>CC</sub> = 5 V               | 2.8<br>2.4 | ns |  |

| C <sub>IN</sub>                      | Input capacitance                    | $V_I = 0 V \text{ or } V_{CC}$                              | 3          | pF |  |

| I <sub>CC</sub>                      | Total supply current                 | Outputs disabled; $V_{CC}$ =5.5 V                           | 2          | μΑ |  |

#### **ORDERING INFORMATION**

| PACKAGES                    | TEMPERATURE RANGE | PART NUMBER | DWG NUMBER |

|-----------------------------|-------------------|-------------|------------|

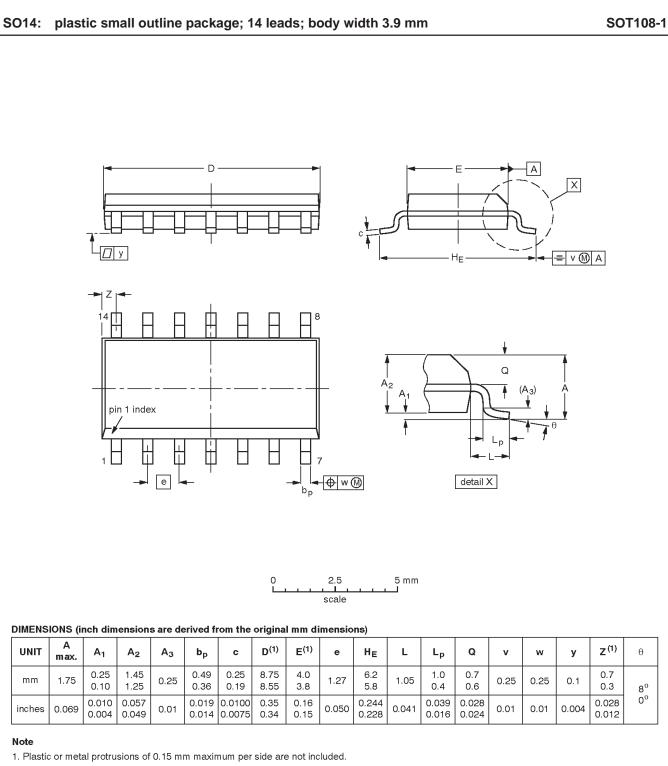

| 14-Pin plastic SO           | −40 °C to +85 °C  | 74ABT5074D  | SOT108-1   |

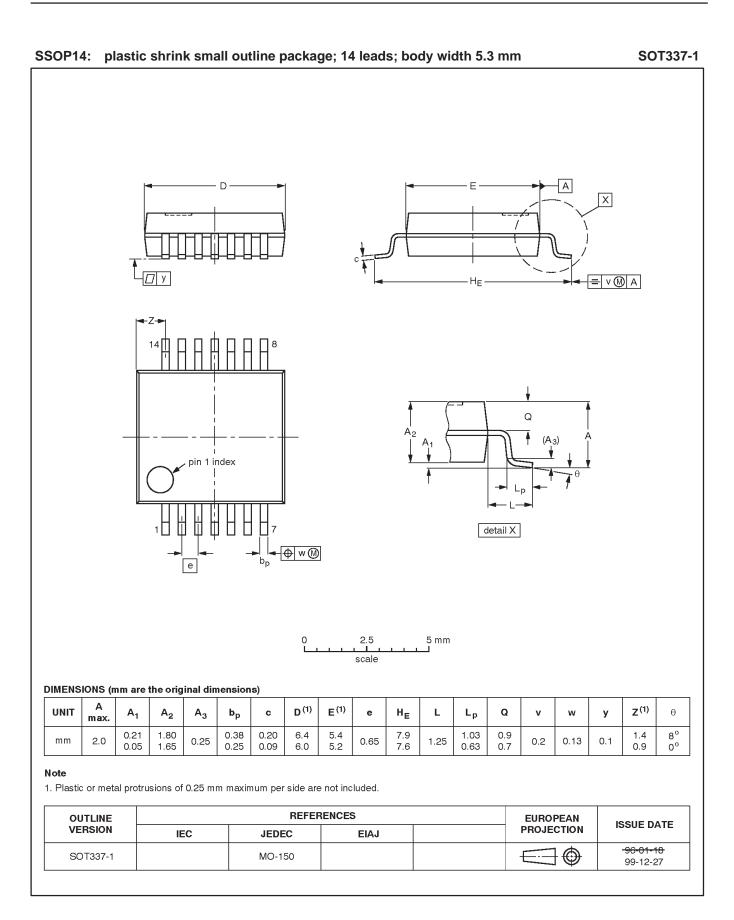

| 14-Pin Plastic SSOP Type II | –40 °C to +85 °C  | 74ABT5074DB | SOT337-1   |

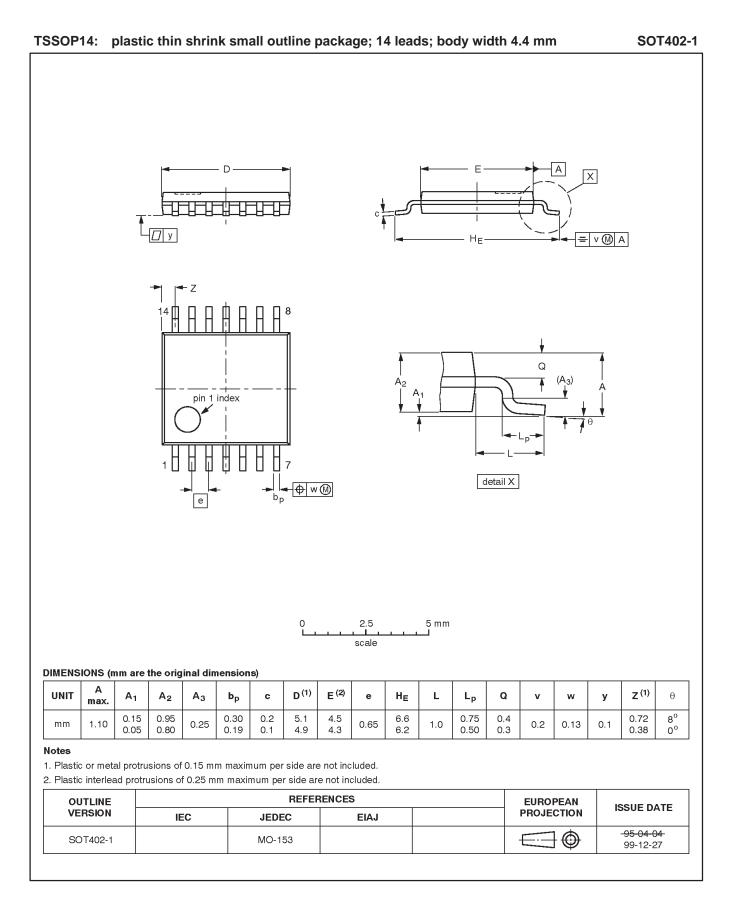

| 14-Pin Plastic TSSOP Type I | –40 °C to +85 °C  | 74ABT5074PW | SOT402-1   |

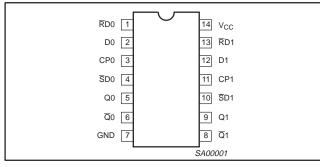

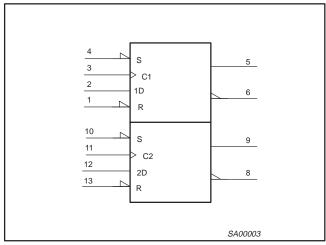

#### **PIN CONFIGURATION**

#### PIN DESCRIPTION

| PIN   | SYMBOL                   | NAME AND FUNCTION                        |

|-------|--------------------------|------------------------------------------|

| 2, 12 | D0, D1                   | Data inputs                              |

| 3, 11 | CP0, CP1                 | Clock inputs (active rising edge)        |

| 4, 10 | <u>S</u> D0, <u>S</u> D1 | Set inputs (active-LOW)                  |

| 1, 13 | RD0, RD1                 | Reset inputs (active-LOW)                |

| 5, 9  | Q0, Q1                   | Data outputs (active-LOW), non-inverting |

| 6, 8  | <u>Q</u> 0, <u>Q</u> 1   | Data outputs (active-LOW), inverting     |

| 7     | GND                      | Ground (0 V)                             |

| 14    | V <sub>CC</sub>          | Positive supply voltage                  |

## 74ABT5074

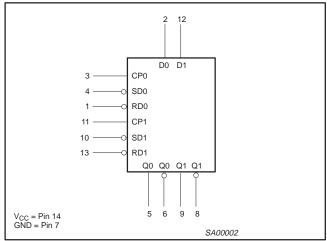

#### LOGIC SYMBOL

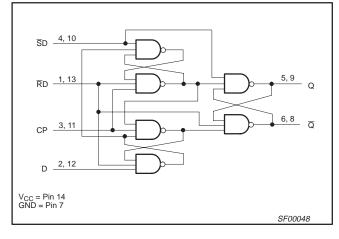

#### LOGIC DIAGRAM

#### **IEC/IEEE SYMBOL**

#### **FUNCTION TABLE**

|    | INPUTS |    |   | OUTPUTS |    | OPERATING          |

|----|--------|----|---|---------|----|--------------------|

| SD | RD     | СР | D | Q       | Q  | MODE               |

| L  | Н      | Х  | Х | Н       | L  | Asynchronous set   |

| Н  | L      | Х  | Х | L       | Н  | Asynchronous reset |

| L  | L      | Х  | Х | L       | Н  | Undetermined*      |

| Н  | Н      | Ŷ  | h | Н       | L  | Load "1"           |

| Н  | Н      | Ŷ  | Ι | L       | Н  | Load "0"           |

| Н  | Н      | ¢  | Х | NC      | NC | Hold               |

|    |        |    |   |         |    |                    |

NOTES:

H = HIGH voltage level h = HIGH voltage level one set-up time prior to LOW-to-HIGH

clock transition L

LOW voltage levelLOW voltage level one set-up time prior to LOW-to-HIGH L clock transition

NC= No change from the previous set-up

X = Don't care  $\uparrow = LOW-to-HI$   $\uparrow = Not LOW-t$

LOW-to-HIGH clock transition

= Not LOW-to-HIGH clock transition

This set-up is unstable and will change when either set or = reset return to the HIGH level

### 74ABT5074

## Synchronizing dual D-type flip-flop with metastable immune characteristics

#### **METASTABLE IMMUNE CHARACTERISTICS**

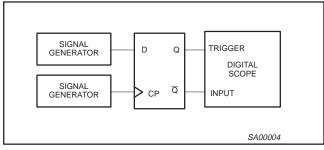

Philips Semiconductors uses the term 'metastable immune' to describe characteristics of some of the products in its family. By running two independent signal generators (see Figure 1) at nearly the same frequency (in this case 10 MHz clock and 10.02 MHz data) the device-under-test can often be driven into a metastable state. If the Q output is then used to trigger a digital scope set to infinite persistence the  $\overline{Q}$  output will build a waveform. An experiment was run by continuously operating the devices in the region where metastability will occur.

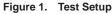

After determining the  $T_0$  and  $\tau$  of the flop, calculating the mean time between failures (MTBF) is simple. Suppose a designer wants to use the 74ABT5074 for synchronizing asynchronous data that is arriving at 10 MHz (as measured by a frequency counter), has a clock frequency of 50 MHz, and has decided that he would like to sample the output of the 74ABT5074 7 nanoseconds after the clock edge. He simply plugs his number into the following equation:

$$MTBF = e^{(t'/\tau)} / T_O^* f_C^* f_I$$

In this formula,  $f_C$  is the frequency of the clock,  $f_I$  is the average input event frequency, and t' is the time after the clock pulse that the output is sampled (t' > h, h being the normal propagation delay). In this situation the  $f_I$  will be twice the data frequency of 20 MHz because input events consist of both of low and high transitions. Multiplying  $f_I$  by  $f_C$  gives an answer of  $10^{15}$  Hz<sup>2</sup>. From Figure 2 it is clear that the MTBF is greater than  $10^{10}$  seconds. Using the above formula the actual MTBF is  $1.69 \times 10^{10}$  seconds or about 535 years.

Figure 2. Mean Time Between Failures (MTBF) versus t'

### 74ABT5074

| N               | T <sub>amb</sub> = −40 °C |                              | -      | Г <sub>атb</sub> = 25 °С     | T <sub>amb</sub> = 85 °C |                                 |

|-----------------|---------------------------|------------------------------|--------|------------------------------|--------------------------|---------------------------------|

| V <sub>cc</sub> | τ                         | Τ <sub>0</sub>               | τ      | Τ <sub>0</sub>               | τ                        | Τ <sub>0</sub>                  |

| 5.5 V           | 84 ps                     | $1.0 	imes 10^6  \text{sec}$ | 93 ps  | $3.8 	imes 10^6  \text{sec}$ | 89 ps                    | $1.5 	imes 10^9  m  sec$        |

| 5.0 V           | 84 ps                     | $2.7 	imes 10^8 \text{ sec}$ | 94 ps  | $1.3 	imes 10^7 \text{ sec}$ | 106 ps                   | $2.2 \times 10^{6} \text{ sec}$ |

| 4.5 V           | 89 ps                     | $1.0 	imes 10^9  m  sec$     | 103 ps | $2.1 	imes 10^7 \text{ sec}$ | 115 ps                   | $4.4 	imes 10^6 \ \mathrm{sec}$ |

#### TYPICAL VALUES FOR $\tau$ AND T<sub>0</sub> AT VARIOUS V<sub>CC</sub>S AND TEMPERATURES

#### ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>

| SYMBOL           | PARAMETER                      | CONDITIONS                  | RATING       | UNIT |

|------------------|--------------------------------|-----------------------------|--------------|------|

| V <sub>CC</sub>  | DC supply voltage              |                             | -0.5 to +7.0 | V    |

| I <sub>IK</sub>  | DC input diode current         | V <sub>I</sub> < 0 V        | -18          | mA   |

| VI               | DC input voltage <sup>3</sup>  |                             | -1.2 to +7.0 | V    |

| I <sub>ОК</sub>  | DC output diode current        | V <sub>O</sub> < 0 V        | -50          | mA   |

| V <sub>OUT</sub> | DC output voltage <sup>3</sup> | Output in Off or HIGH state | -0.5 to +5.5 | V    |

| I <sub>OUT</sub> | DC output current              | Output in LOW state         | 40           | mA   |

| T <sub>stg</sub> | Storage temperature range      |                             | –65 to 150   | °C   |

NOTES:

Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150 °C.

3. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

#### **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL           | PARAMETER                                              | LIM | UNIT            |      |

|------------------|--------------------------------------------------------|-----|-----------------|------|

| STWBOL           | PARAMETER                                              | MIN | MAX             | UNIT |

| V <sub>CC</sub>  | DC supply voltage                                      |     | 5.5             | V    |

| VI               | Input voltage                                          | 0   | V <sub>CC</sub> | V    |

| V <sub>IH</sub>  | HIGH-level input voltage                               | 2.0 | -               | V    |

| V <sub>IL</sub>  | LOW-level Input voltage                                | -   | 0.8             | V    |

| I <sub>ОН</sub>  | HIGH-level output current                              | -   | -15             | mA   |

| I <sub>OL</sub>  | LOW-level output current                               | -   | 20              | mA   |

| Δt/Δv            | $\Delta t/\Delta v$ Input transition rise or fall rate |     | 10              | ns/V |

| T <sub>amb</sub> | T <sub>amb</sub> Operating free-air temperature range  |     | +85             | °C   |

### DC ELECTRICAL CHARACTERISTICS

|                  |                                                      |                                                                                 | LIMITS                    |       |      |                          |              |      |

|------------------|------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------|-------|------|--------------------------|--------------|------|

| SYMBOL           | PARAMETER                                            | TEST CONDITIONS                                                                 | T <sub>amb</sub> = +25 °C |       |      | T <sub>amb</sub> = -40 ° | °C to +85 °C | UNIT |

|                  |                                                      |                                                                                 | MIN                       | ТҮР   | MAX  | MIN                      | MAX          |      |

| V <sub>IK</sub>  | Input clamp voltage                                  | V <sub>CC</sub> = 4.5 V; I <sub>IK</sub> = -18 mA                               | -                         | -0.9  | -1.2 | -                        | -1.2         | V    |

| V <sub>OH</sub>  | HIGH-level output voltage                            | $V_{CC}$ = 4.5 V; $I_{OH}$ = –15 mA; $V_{I}$ = $V_{IL}$ or $V_{IH}$             | 2.5                       | 2.9   | _    | 2.5                      | -            | V    |

| V <sub>OL</sub>  | LOW-level output voltage                             |                                                                                 | -                         | 0.35  | 0.5  | -                        | 0.5          | V    |

| I <sub>I</sub>   | Input leakage current                                | $V_{CC}$ = 5.5 V; $V_{I}$ = GND or 5.5 V                                        | -                         | ±0.01 | ±1.0 | -                        | ±1.0         | μΑ   |

| I <sub>OFF</sub> | Power-off leakage current                            | $V_{CC}$ = 0.0 V; $V_{O}$ or $V_{I}\leq4.5$ V                                   | -                         | ±5.0  | ±100 | -                        | ±100         | μΑ   |

| Ι <sub>Ο</sub>   | Output current <sup>1</sup>                          | V <sub>CC</sub> = 5.5 V; V <sub>O</sub> = 2.5 V                                 | -50                       | -75   | -180 | -50                      | -180         | mA   |

| I <sub>CC</sub>  | Quiescent supply current                             | $V_{CC}$ = 5.5 V; $V_{I}$ = GND or $V_{CC}$                                     | -                         | 2     | 50   | -                        | 50           | μΑ   |

| $\Delta I_{CC}$  | Additional supply current per input pin <sup>2</sup> | $V_{CC}$ = 5.5 V; one input at 3.4 V,<br>other inputs at V <sub>CC</sub> or GND |                           | 0.25  | 500  | -                        | 500          | μA   |

#### NOTES:

1. Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

2. This is the increase in supply current for each input at 3.4 V.

#### **AC CHARACTERISTICS**

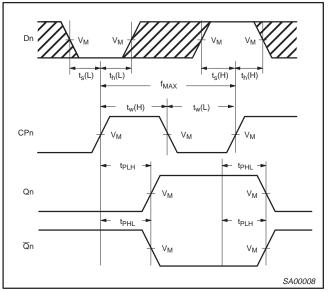

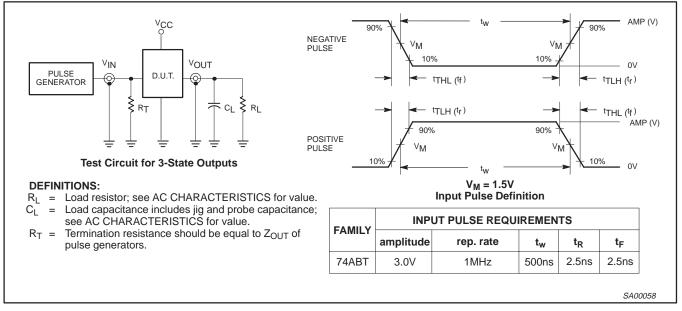

GND = 0 V,  $t_R = t_F$  = 2.5 ns,  $C_L$  = 50 pF,  $R_L$  = 500  $\Omega$

|                                      |                                                |          | LIMITS                                                |            |            |                                                 |            |    |

|--------------------------------------|------------------------------------------------|----------|-------------------------------------------------------|------------|------------|-------------------------------------------------|------------|----|

| SYMBOL                               | PARAMETER                                      | WAVEFORM | T <sub>amb</sub> = +25 °C<br>V <sub>CC</sub> = +5.0 V |            |            | $T_{amb} = -40^{\circ}$ $V_{CC} = +5.0^{\circ}$ | UNIT       |    |

|                                      |                                                |          | MIN                                                   | ТҮР        | MAX        | MIN                                             | MAX        |    |

| f <sub>max</sub>                     | Maximum clock frequency                        | 1        | 180                                                   | 250        | -          | 150                                             | -          | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>CPn to Qn or Qn           | 1        | 1.0<br>1.0                                            | 2.8<br>2.4 | 3.9<br>3.5 | 1.0<br>1.0                                      | 4.5<br>3.7 | ns |

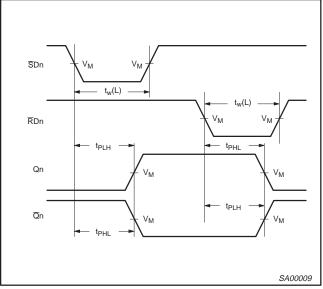

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>SDn, RDn_to Qn or Qn      | 2        | 1.0<br>1.0                                            | 3.5<br>3.1 | 4.6<br>4.2 | 1.0<br>1.0                                      | 5.5<br>4.7 | ns |

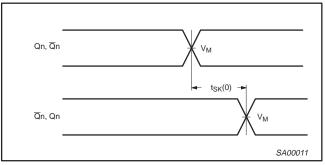

| t <sub>sk(o)</sub>                   | Output skew <sup>1, 2</sup><br>CPn to Qn to Qn | 4        | -                                                     | -          | 1.5        | -                                               | 2.0        | ns |

NOTES:

1.  $|t_{PN} \text{ actual} - t_{PM} \text{ actual} |$  for any output compared to any other output where N and M are either LH or HL. 2. Skew times are valid only under same test conditions (temperature, V<sub>CC</sub>, loading, etc.).

#### AC SET-UP REQUIREMENTS

GND = 0 V,  $t_{R}$  =  $t_{F}$  = 2.5 ns,  $C_{L}$  = 50 pF,  $R_{L}$  = 500  $\Omega$

|                                          |                                                         |          |                                         | LIMI             | TS                                                                                                                         |      |

|------------------------------------------|---------------------------------------------------------|----------|-----------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------|------|

| SYMBOL                                   | PARAMETER                                               | WAVEFORM | T <sub>amb</sub> =<br>V <sub>CC</sub> = | +25 °C<br>+5.0 V | $\begin{array}{l} {T_{amb}} = -40 \ ^{\circ}{C} \ to \ +85 \ ^{\circ}{C} \\ {V_{CC}} = +5.0 \ V \ \pm 0.5 \ V \end{array}$ | UNIT |

|                                          |                                                         |          | MIN                                     | ТҮР              | MIN                                                                                                                        |      |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Set-up time, HIGH or LOW<br>Dn to CPn                   | 1        | 2.5<br>2.5                              | 1.5<br>1.5       | 2.5<br>2.5                                                                                                                 | ns   |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time, HIGH or LOW<br>Dn to CPn                     | 1        | 0<br>0                                  | -1.4<br>-1.4     | 0<br>0                                                                                                                     | ns   |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CPn pulse width,<br>HIGH or LOW                         | 1        | 1.5<br>2.4                              | 0.6<br>1.8       | 1.5<br>2.9                                                                                                                 | ns   |

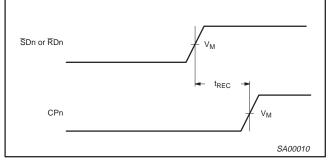

| t <sub>w</sub> (L)                       | $\overline{S}$ Dn or $\overline{R}$ Dn pulse width, LOW | 2        | 2.0                                     | 1.3              | 2.2                                                                                                                        | ns   |

| t <sub>rec</sub>                         | Recovery time<br>SDn or RDn to CPn                      | 3        | 2.4                                     | 1.3              | 2.8                                                                                                                        | ns   |

## 74ABT5074

## Product data

## 74ABT5074

#### AC WAVEFORMS

$V_{M}$  = 1.5 V,  $V_{IN}$  = GND to 3.0 V

The shaded areas indicate when the input is permitted to change for the predictable output performance.

Waveform 3. Recovery Time for Set or Reset to Output

Waveform 2. Propagation Delay for Set and Reset to Output, Set and Reset Pulse Width

Waveform 4. Output Skew

2002 Dec 17

## 74ABT5074

#### **TEST CIRCUIT AND WAVEFORM**

Product data

## 74ABT5074

| OUTLINE  |        | REFERENCES |      |  | EUROPEAN   | ISSUE DATE                       |

|----------|--------|------------|------|--|------------|----------------------------------|

| VERSION  | IEC    | JEDEC      | EIAJ |  | PROJECTION | ISSUE DATE                       |

| SOT108-1 | 076E06 | MS-012     |      |  |            | <del>-97-05-22</del><br>99-12-27 |

## 74ABT5074

Product data

### 74ABT5074

## 74ABT5074

#### **REVISION HISTORY**

| Rev | Date     | Description                                                                                                  |  |  |  |

|-----|----------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| _2  | 20021217 | roduct data (9397 750 10847); ECN 853-1775 29293 of 12 December 2002.<br>upersedes data of 15 December 1994. |  |  |  |

|     |          | lifications:                                                                                                 |  |  |  |

|     |          | <ul> <li>Ordering information table: remove 74ABT5074N package offering.</li> </ul>                          |  |  |  |

| _1  | 19941215 | Product specification. ECN 853-1775 14470 of 15 December 1994.                                               |  |  |  |

### 74ABT5074

#### Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.<br>Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                 |

| 11    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| 111   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

[3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax:

Fax: +31 40 27 24825

© Koninklijke Philips Electronics N.V. 2002 All rights reserved. Printed in U.S.A.

Date of release: 12-02

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com

Document order number:

9397 750 10847

Let's make things better.